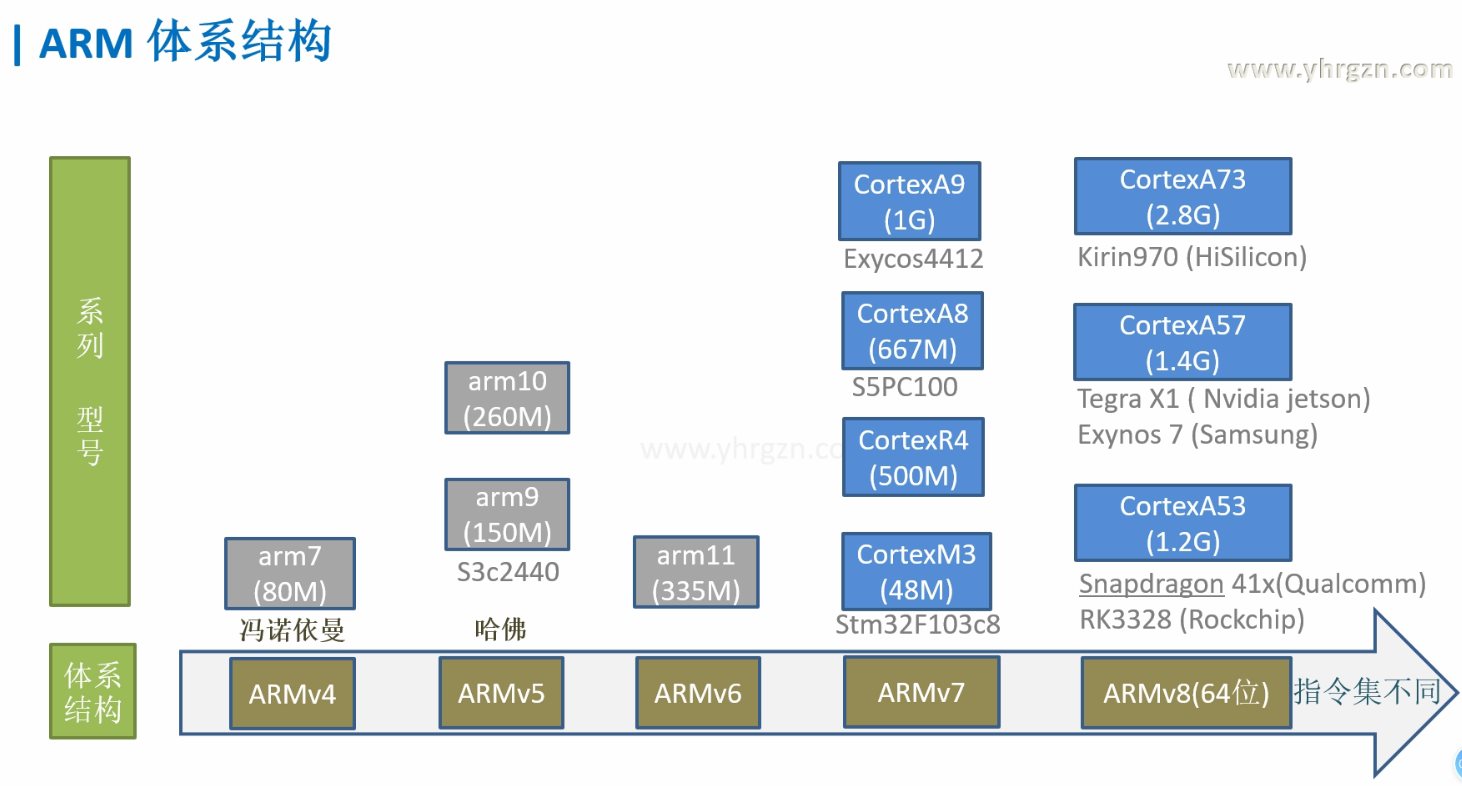

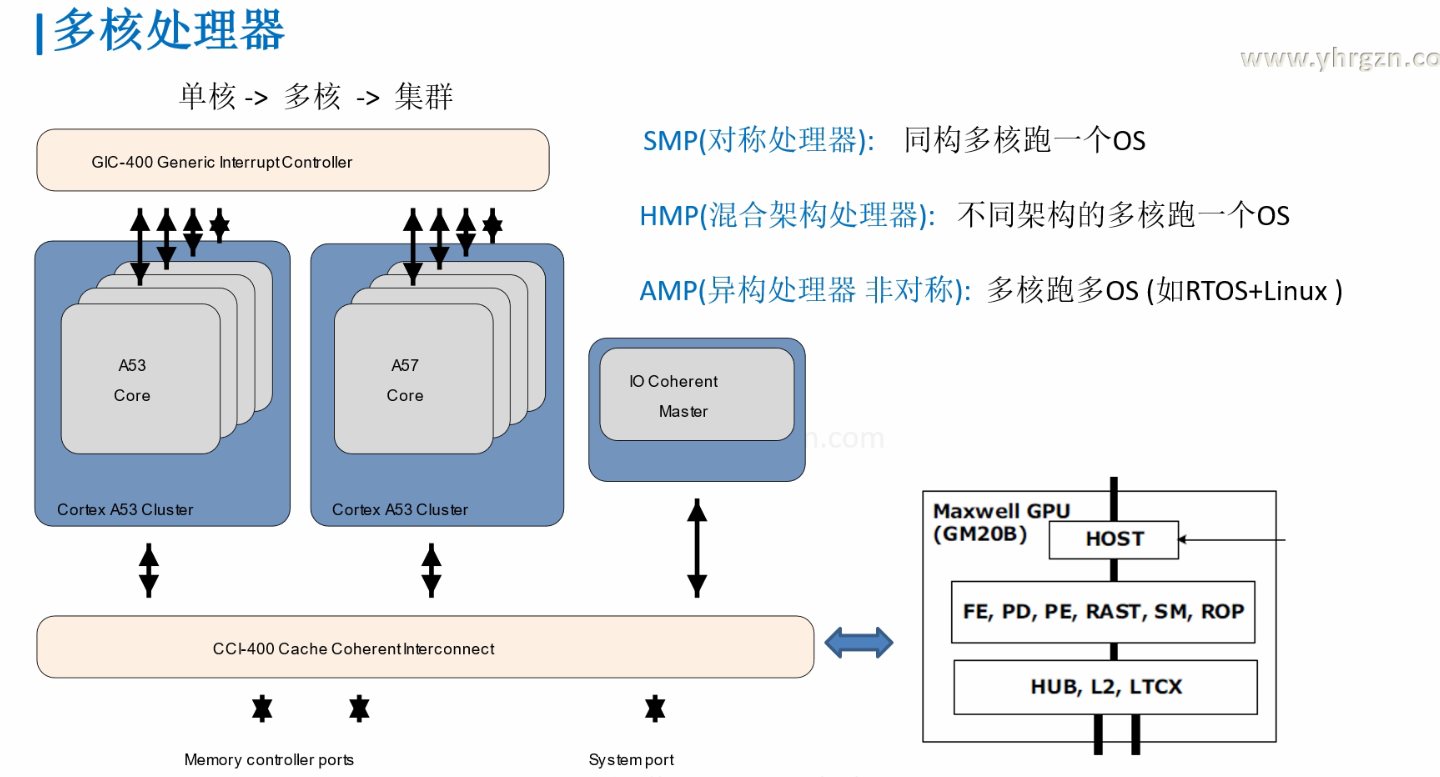

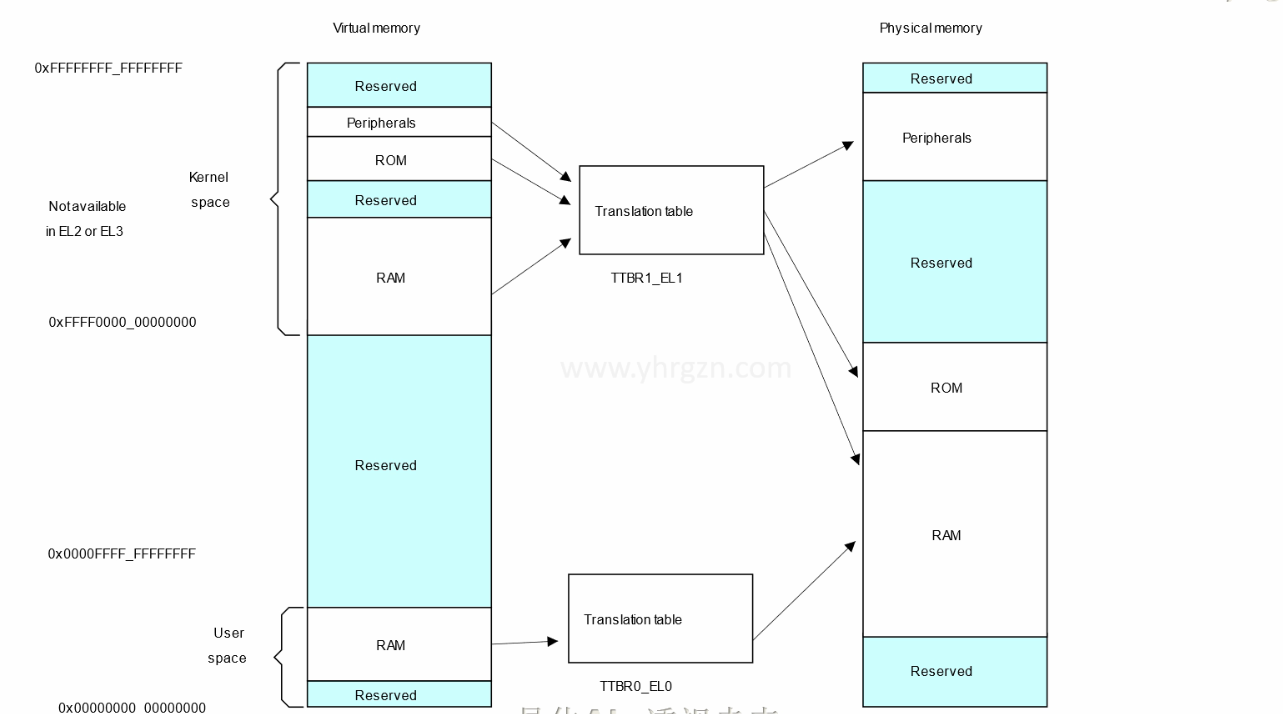

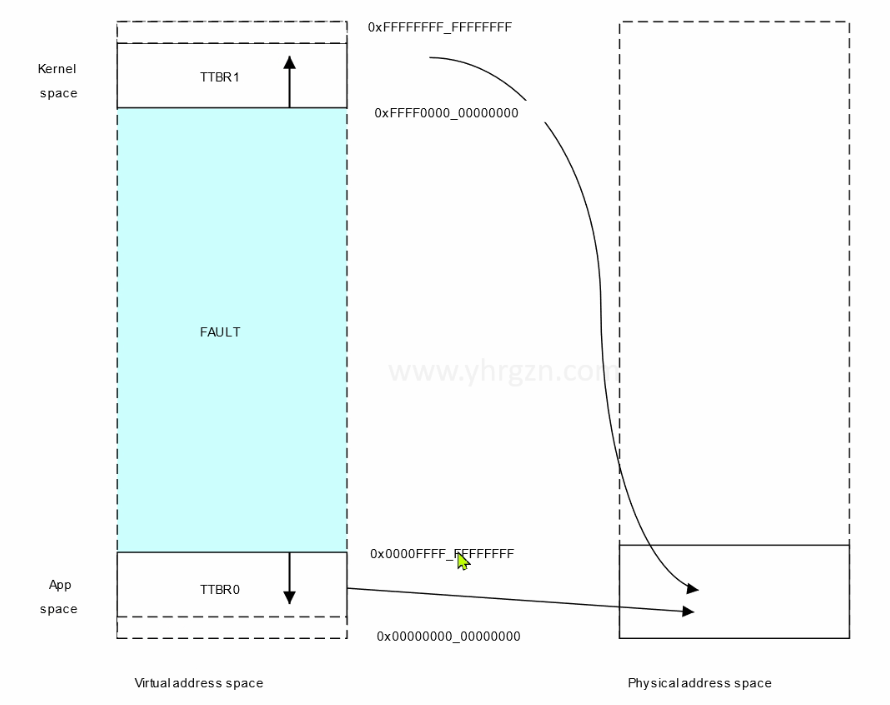

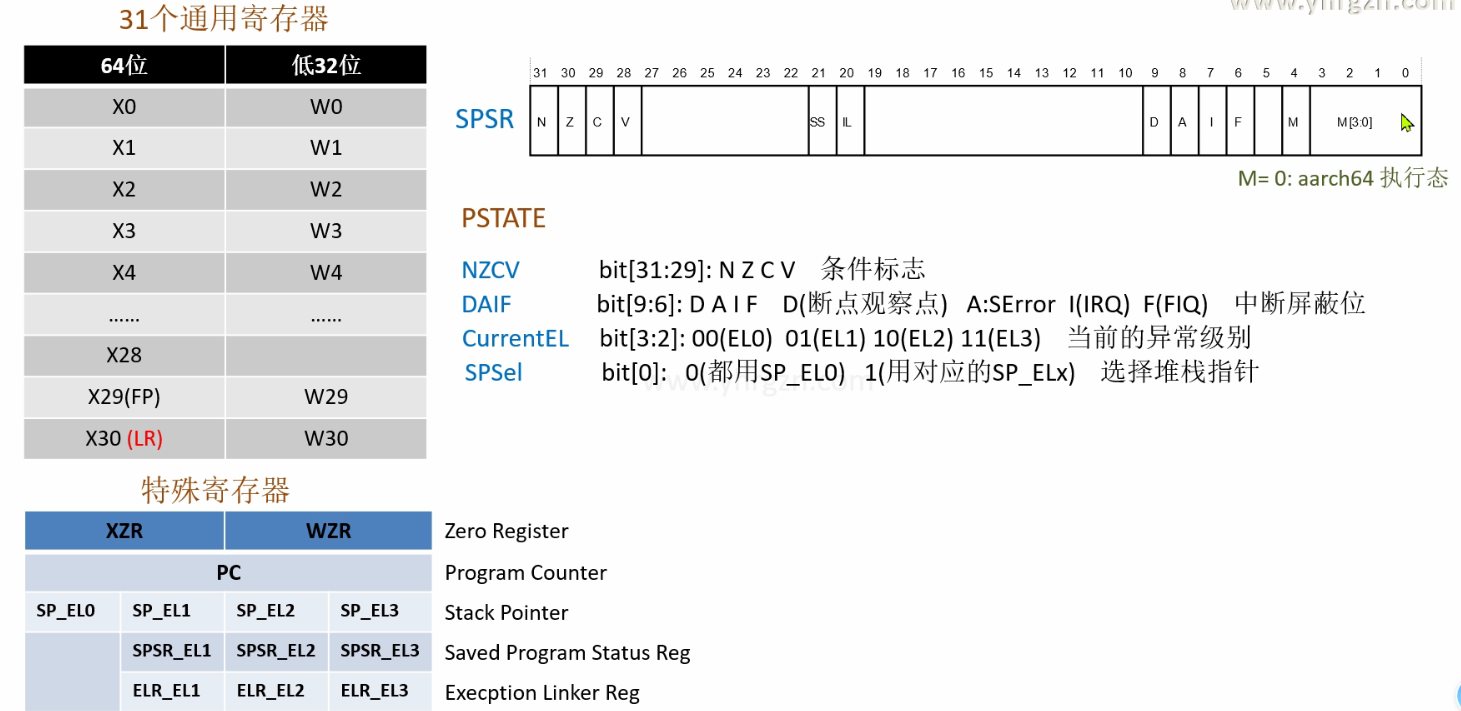

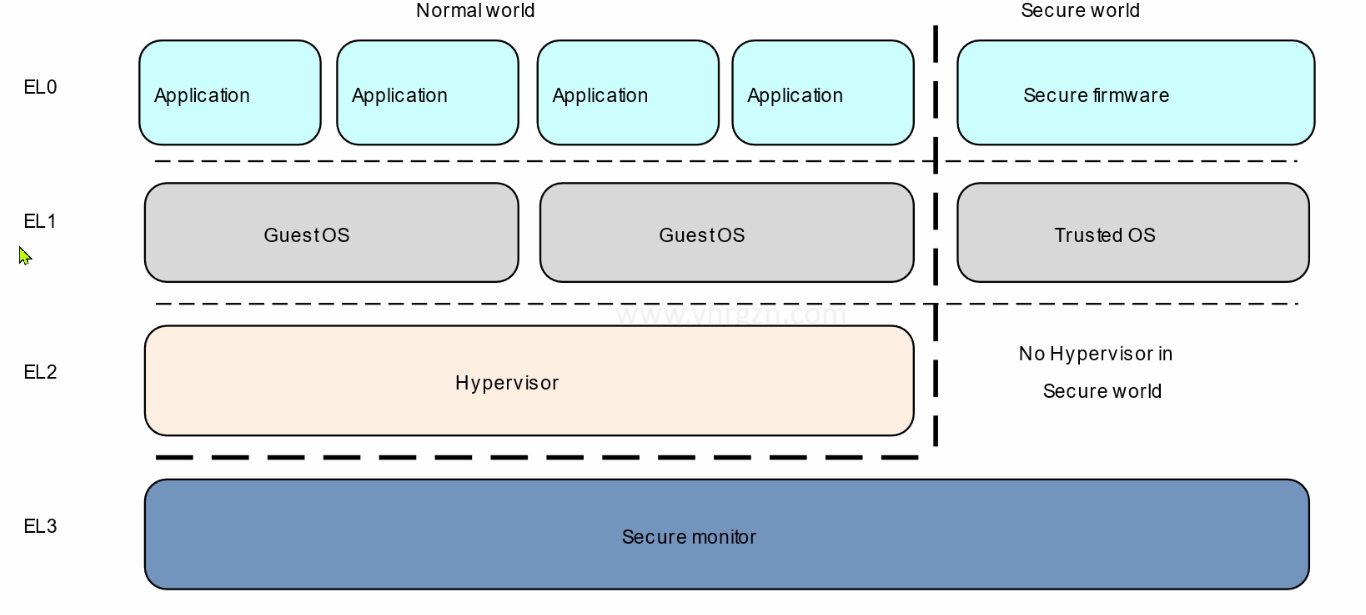

ARM8 64位汇编简介 电脑版发表于:2024/7/1 22:19  >#ARM8 64位汇编简介 [TOC] 版本差异 ------------ |特性| ARM7| ARM8| | ------------ | ------------ | |内存 |仅支持 32 位地址空间| 支持 64 位和 32 位地址空间| |虚拟化| 不支持硬件虚拟化| 支持硬件虚拟化,包括虚拟化扩展和高效虚拟机管理| |安全| 较少的安全特性,主要依赖软件实现| 增强的安全特性,如 ARM TrustZone| |执行状态| 仅支持 32 位执行状态| 支持 64 位和 32 位执行状态| |异常级别| 不支持多级异常级别,仅有一个特权级别| 支持多个异常级别,包括 EL0 (用户), EL1 (内核), EL2 (虚拟化), EL3 (安全监控)| |安全模式| 不支持硬件级别安全模式,依赖软件保护| 支持 ARM TrustZone 安全模式,提供硬件隔离| |主要用途| 嵌入式系统和简单消费电子产品| 高性能计算设备、服务器、桌面计算机、高端嵌入式系统|  tn2>一般未来一些高端设备都是armv8进行开发。  多核处理器 ------------  | 类型 | 解释 | 优势 | 适用场景 | |---------------|-----------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------| | 单核处理器 | 只有一个处理核心 | - 设计、实现和调试相对简单<br>- 制造成本和功耗较低 | 嵌入式系统中的单一任务 | | 多核处理器 | 有多个处理核心,可以同时执行多个任务 | - 能够同时处理多个任务,提高整体系统的性能<br>- 多个核心分担任务,响应时间更快<br>- 降低单个核心的频率和功耗 | 智能手机、服务器等需要高并发处理的场景 | | 同构多核 (SMP)| 多个相同架构的核心运行一个操作系统 | - 所有核心平等地处理任务,容易实现负载均衡<br>- 开发者可以将任务均匀分配到各个核心,无需考虑核心差异 | 通用计算设备、服务器等多任务处理系统 | | 混合架构多核 (HMP) | 不同架构的多个核心运行一个操作系统 | - 高性能核心处理重任务,低功耗核心处理轻任务,达到性能和功耗的最佳平衡<br>- 动态分配核心,提高系统效率 | 需要在高性能和低功耗之间动态切换的设备,如智能手机 | | 异构处理器 (AMP) | 多个不同架构的核心运行多个操作系统 | - 每个核心可以独立运行不同的操作系统和任务,互不干扰<br>- 将特定任务分配给最适合的核心,提高处理效率 | 工业控制、航空航天等需要同时运行多个实时和非实时操作系统的场景 | 内存管理单元MMU ------------  tn2>这是一张内存管理图,左边是虚拟内存右边是物理内存。 中间的`Translation table`(转换表)负责将虚拟地址转换为物理地址。 ### 虚拟内存(Virtual Memory) tn2>虚拟内存的上部分(`0xFFFFFFFF_FFFFFFFF` 到 `0xFFFF0000_00000000`) | | 用途 | 举例 | | ------------ | ------------ | ------------ | | 保留区(Reserved) | 保留区通常是为将来扩展或特殊用途保留的内存地址,不会被一般程序使用。 | 操作系统可能会在这里预留一些空间用于内核数据结构或高级功能,比如内存镜像。 | | 外设(Peripherals) | 用于映射硬件设备的地址,使CPU可以通过读写这些地址来控制设备。 | 一个计算机的网络接口卡(NIC)或图形处理单元(GPU)的控制寄存器会映射到这里,操作系统通过访问这些地址来发送网络数据或渲染图像。 | | ROM | 存储只读数据,通常是系统启动时需要的固件或初始化代码。 | 计算机的BIOS或UEFI固件存储在ROM中,开机时,CPU从ROM中读取启动指令来初始化系统。 | | 保留区(Reserved) | 同上,预留的内存地址空间。 | 可能用于特定的内核功能或扩展,例如高级安全功能的实现。 | | RAM | 存储正在运行的程序和数据。 | 运行中的应用程序,如浏览器、文本编辑器,它们的代码和数据都会存放在RAM中。 | tn2>虚拟内存的下部分(`0x0000FFFF_FFFFFFFF` 到 `0x00000000_00000000`) | | 用途 | 举例 | | ------------ | ------------ | ------------ | | 保留区(Reserved) | 预留的内存地址空间。 | 可能用于用户空间中的特定用途,例如高级用户模式驱动程序或应用的扩展模块。 | | RAM | 同上,存储正在运行的程序和数据。 | 用户态的应用程序,如游戏或办公软件,它们运行时需要大量内存,都会在这里分配。| ### 物理内存(Physical Memory) tn2>物理内存的上部分 | | 用途 | 举例 | | ------------ | ------------ | ------------ | | 保留区(Reserved) | 预留的物理内存,不被一般应用程序直接使用。 | 系统保留用于特定用途,如热插拔内存设备的地址空间。 | | 外设(Peripherals) | 物理设备的地址映射区域。 | 计算机中的声卡、网卡等设备的物理地址。| | 保留区(Reserved) | 预留的物理内存地址空间。 | 用于高级内存管理功能或操作系统特定用途。| | ROM | 存储只读数据,如固件和启动代码。 | 计算机的启动固件存储在这里,系统启动时从这里读取初始化指令。| | RAM | 实际使用的物理内存。 | 运行中的程序和数据在这里存储。| tn2>物理内存的下部分 | | 用途 | 举例 | | ------------ | ------------ | ------------ | | 保留区(Reserved) | 预留的物理内存地址空间。 | 可能用于高级内存管理功能,确保内存分配的灵活性和安全性。 | | RAM | 实际使用的物理内存。 | 操作系统和应用程序的实际数据存储在这里,包括内核、堆、栈等。| ### 地址转换表(Translation Table) tn2>用途:这些寄存器保存翻译表的基地址,用于将虚拟地址映射到物理地址。 举例:当CPU访问一个虚拟地址时,MMU使用这些寄存器中的翻译表来查找对应的物理地址。 例如,用户态程序访问某个数据时,MMU通过TTBR0_EL0将虚拟地址转换为物理地址。  tn2>这张图展示了虚拟地址空间到物理地址空间的映射,特别是两个不同的翻译基地址寄存器(Translation Table Base Register,TTBR)的工作情况。 | | 用途 | 举例 | | ------------ | ------------ | ------------ | | TTBR1 | 用于管理内核态的地址空间。 | 操作系统内核代码和数据会被映射到物理地址上,使得内核可以正常工作和运行。 | | FAULT | 作为保护机制,防止非法访问。 |表示这是一个无效区域,如果访问到这里会引发一个页面错误(page fault)。| tn2>上边都是内核空间,下面是应用空间。 | | 用途 | 举例 | | ------------ | ------------ | ------------ | | TTBR0 | 这是另一个翻译表基地址寄存器,专门用于用户态(应用程序空间)的地址映射。 | 用户运行的应用程序,比如浏览器、文本编辑器等,它们的虚拟地址通过这个翻译表映射到物理内存。 | tn2>图片右边展示的是物理地址空间,这里表示了虚拟地址是如何被映射到实际的物理内存地址的。 虚拟地址(0xFFFFFFFF_FFFFFFFF 到 0xFFFF0000_00000000):这段虚拟地址通过TTBR1(内核态)翻译表映射到物理地址空间。 虚拟地址(0x0000FFFF_FFFFFFFF 到 0x00000000_00000000):这段虚拟地址通过TTBR0(用户态)翻译表映射到物理地址空间。 ARM8寄存器 ------------  ### 通用寄存器 tn2>这些是CPU中最常用的数据存储单元。想象它们是CPU的小笔记本,可以快速记录和读取数据。每个寄存器都有两种模式: 64位模式 (X0-X30): 可以存储更大的数字 32位模式 (W0-W30): 存储较小的数字,但处理速度可能更快 tn>需要注意的是,X29 通常用作帧指针(FP),X30 通常用作链接寄存器(LR),存储函数返回地址 ### SPSR寄存器 tn2>这个寄存器就像是CPU的"心情日记"。它记录了当前程序运行的各种状态: NZCV: 这些是条件标志,告诉CPU上一个操作的结果(是否为负,是否为零等) DAIF: 这些位控制不同类型的中断(类似于CPU的"勿扰模式") CurrentEL: 表示当前的特权级别,决定程序能做什么不能做什么 SPSel: 选择使用哪个栈指针 ### 特殊寄存器 tn2>ZR (零寄存器): 永远返回0,用于一些特殊操作,列如目标寄存器时丢弃结果。 SP(堆栈指针):管理函数调用和局部变量,SP指向顶部 PC (程序计数器): 指向下一条要执行的指令,像是CPU的"阅读指针" SPSR和ELR: 在处理异常(如中断)时使用,保存正常执行时的状态 tn>在ARM8中有4个异常级别,从EL0-EL3  | 异常级别 | 描述 | | ------------ | ------------ | |EL0| 用户级别,运行普通应用程序| |EL1| 操作系统级别| |EL2| 虚拟化层级别| |EL3| 最高权限级别,通常用于安全监控| tn2>每个异常级别都有自己的栈指针 分别对应如下列表。 | 异常级别栈指针 | 描述 | | ------------ | ------------ | |SP_EL0| 用户程序的栈指针| |SP_EL1| 操作系统的栈指针| |SP_EL2| 虚拟化层的栈指针| |SP_EL3| 安全监控的栈指针| tn2>保存的程序状态寄存器 (SPSR): SPSR_EL1, SPSR_EL2, SPSR_EL3: 这些寄存器用于在异常发生时保存程序状态。当从较低级别切换到较高级别时,当前的程序状态会被保存在相应的SPSR中。 异常链接寄存器 (ELR): ELR_EL1, ELR_EL2, ELR_EL3: 这些寄存器保存了发生异常时的返回地址。当异常处理完成后,处理器使用这个地址返回到原来的执行点 ### PSTATE (处理器状态) tn2>PSTATE (处理器状态)这是更详细的CPU状态描述,包括: 条件标志 (NZCV) 中断控制位 (DAIF) 当前执行级别 以及其他控制位 ### 系统寄存器  ### AArch64到AArch32寄存器映射(向前兼容)